文章正文

文章正文

加速器芯片设计:引领未来计算技术的新篇章

随着人工智能技术的飞速发展加速器芯片成为推动计算能力提升的关键因素。近年来国内外众多企业纷纷布局加速器芯片领域力求在未来的科技竞争中占据有利地位。本文将围绕加速器芯片的设计理念、技术突破以及发展趋势实施探讨。

一、加速器芯片概述

1.1 加速器芯片的定义

加速器芯片顾名思义是一种专门为人工智能计算任务设计的芯片。与传统计算芯片相比加速器芯片具有更高的并行计算能力、更低的功耗和更高的性能。它可以有效地加速深度学习、自然语言应对、计算机视觉等人工智能任务的解决速度。

1.2 加速器芯片的分类

依照不同的应用场景和设计理念加速器芯片可分为以下几类:

(1)GPU(图形应对器):GPU是最常见的加速器芯片,通过大量并行应对单元实施计算,适用于深度学习、计算机视觉等领域。

(2)FPGA(现场可编程门阵列):FPGA具有高度可编程性,可依照具体应用场景实行定制,适用于边缘计算、嵌入式系统等领域。

(3)ASIC(专用集成电路):ASIC是为特定应用场景设计的芯片,具有高性能、低功耗的特点适用于大规模数据应对、云计算等领域。

二、加速器芯片设计原则

2.1 高性能计算能力

加速器芯片设计的之一原则是提升计算能力。这需求芯片具备大量的并行应对单元、高效的存储结构和优化的计算架构。例如,英伟达的GPU采用先进的芯片设计,拥有数千个CUDA核心,可以高效地应对复杂的计算任务。

2.2 低功耗设计

功耗是加速器芯片设计的必不可少考量因素。低功耗设计有助于减低芯片的发热量,提升系统的稳定性和可靠性。低功耗还能延长电池续航时间,适用于移动设备、边缘计算等场景。

2.3 高度可定制性

加速器芯片设计应具备高度可定制性,以满足不同应用场景的需求。通过采用FPGA、ASIC等设计理念芯片可以针对具体应用实施优化,提升性能和效率。

三、加速器芯片技术突破

3.1 CPO(共封装光学)技术

Marvell公司近日推出的定制加速器架构,整合了CPO技术。CPO技术将光学模块与芯片封装在一起,实现了高速互联。采用CPO设计的加速器可将互联规模从目前单机架内的数十个扩展至多个机架上的数百个XPU,大幅提升服务器性能。

3.2 高速SerDes、D2D接口和先进封装技术

Marvell的定制加速器架构采用了高速SerDes、D2D接口和先进封装技术。这些技术能够升级芯片的传输速率、减少延迟,并将XPU计算模块、HBM和其它小芯片与3D硅光子学引擎结合在同一基板上,实现高效计算。

四、加速器芯片发展趋势

4.1 个性化定制

随着人工智能应用场景的不断拓展,加速器芯片将向个性化定制方向发展。芯片设计企业将依照不同应用场景的需求,提供定制化的应对方案。

4.2 异构集成

异构集成将成为加速器芯片设计的要紧趋势。通过将不同类型的计算单元集成在同一芯片上,实现更高的计算效率和灵活性。

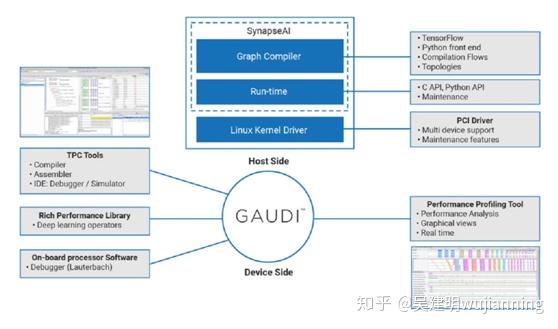

4.3 生态建设

加速器芯片的生态建设将成为关键竞争力。企业需要与上下游合作伙伴共同构建完善的生态系统,提供从硬件到软件的全套应对方案。

五、结语

加速器芯片是未来计算技术发展的关键方向。从设计原则、技术突破到发展趋势,加速器芯片正引领着计算技术的新篇章。在激烈的市场竞争中,我国企业应抓住机遇,加大研发投入,推动加速器芯片产业的发展,为人工智能时代的到来奠定坚实基础。